- PTBLite TSU¿˚”√Zynq GMAC÷–∞¸∫¨µƒPTPΩ‚Œˆ∆˜£¨“‘ π”√ð^…ŸµƒFPGAŸY‘¥ÅÌ÷π©TSU£¨µ´PS GMAC…œµƒIEEE 1588”≤þBæÄþâðã ©º”¡À“ª–©œÞ÷∆°£

É…∑N∞ʱ浃TSU∂ºø…“‘ π”√É»≤øø…’{∂®ïr∆˜ªÚ胡̓ªÇÄTSU´@»°∆‰∂®ïr∆˜÷µ°£“Ú¥À£¨∂ýÇÄ“‘ôæWþBΩ”ø…“‘π≤œÌÕ¨“ª”ãïr∆˜£¨ªÚ’þ≤ªÕ¨µƒ“‘ôæWþBΩ”ø…“‘æþ”–∏˜◊‘µƒ”ãïr∆˜°£

- Ðõº˛PTPÖ¢øº‘O”ã°£SoC-e÷π©¡ÀLinuxÉ»∫À—a∂°£¨‘ì—a∂°‘ ‘S π”√Linux PTP”≤º˛ïrÁ䣮PHC£©◊”œµΩy‘LÜñTSU°£þÄ÷π©¡Àéß”–∆‰À˚π¶ƒÐµƒÈ_‘¥LinuxPTPÐõº˛∂—󣵃–Þ∏ƒ∞ʱ氣”…”⁄∆‰ƒ£âKªØ‘O”㣨“∆÷≤µΩ∆‰À˚≤Ÿ◊˜ «ø…––µƒ°£

“‘œ¬Xilinx FPGAœµ¡–ø…“‘÷ß≥÷æ´¥_ïrÈgª˘µA£∫

- 7œµ¡–£®Zynq£¨Spartan£¨Artix£¨Kintex£¨Virtex£©

- Ultrascale£®Kintex£¨Virtex£©

- Ultrascale +£®Zynq MPSoC£¨Kintex£¨Virtex£©

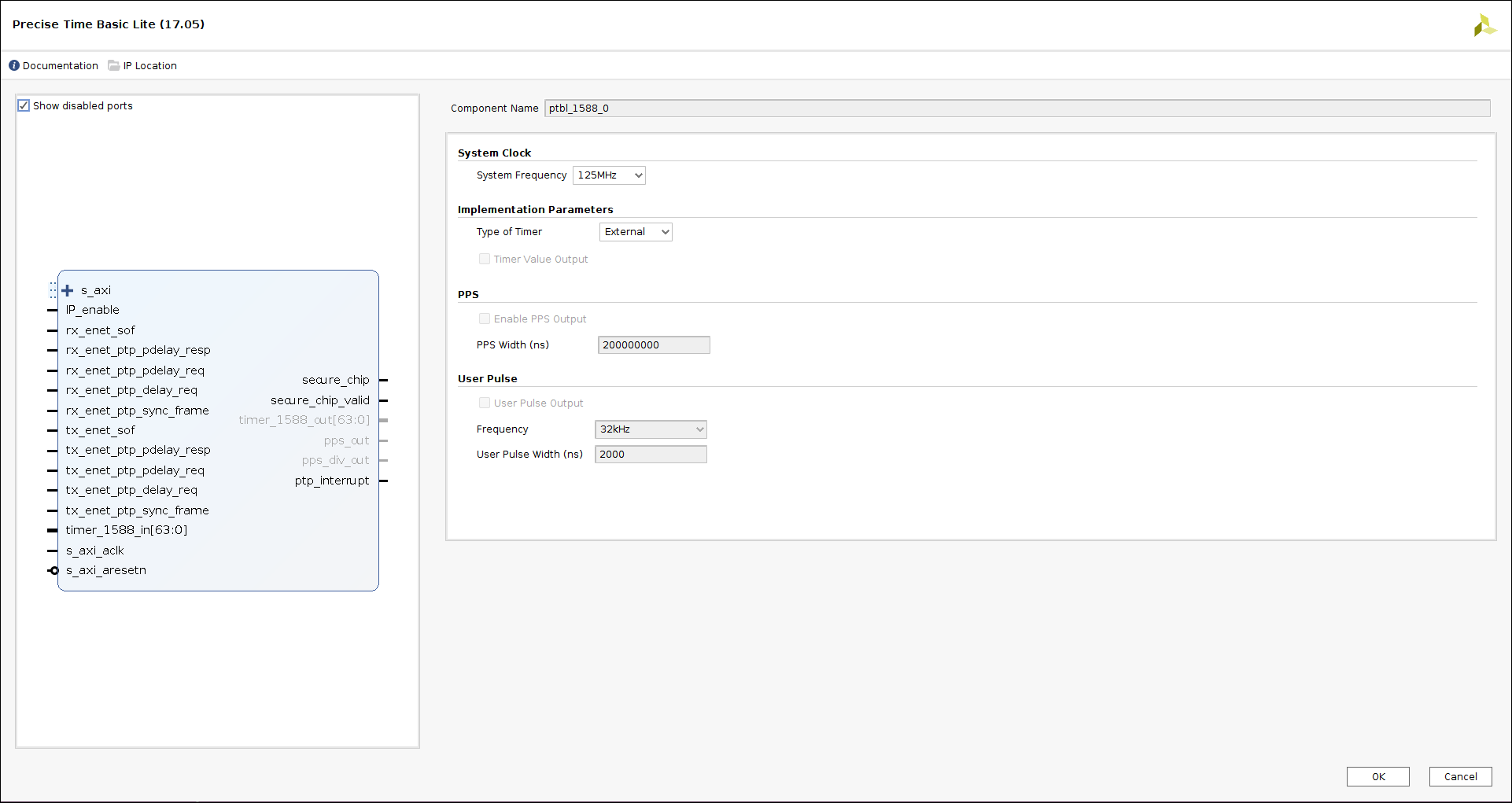

Õ®þ^¿˚”√–¬µƒXilinx Vivadoπ§æþ£¨ø…“‘ðpÀ…µÿå¢∆‰ºØ≥…µΩƒ„µƒFPGA‘O”ã÷–£¨‘ìπ§æþ‘ ‘S‘⁄àD–Œ”√ëÙΩÁ√Ê÷– π”√IPÉ»∫À£¨≤¢“‘∫ܱ„µƒ∑Ω Ω≈‰÷√IP֢£

æ´¥_ïrÈgª˘µAIP∫Àµƒ÷˜“™π¶ƒÐ£∫

”≤º˛π¶ƒÐ£∫

- ÷ß≥÷10/100/1000Mbps/AXI-Stream£®”√”⁄10Gbps/25Gbps£©Ω”ø⁄

- 32Œª√Î/32Œªº{√Δãîµ∆˜

- 32ŒªÅܺ{√ÎÓl¬ ’{’˚

- √ø√Γª√}õ_ðî≥ˆ

- ø…þxÓl¬ ðî≥ˆ£®1 KHz/2 KHz/4 KHz/8 KHz/16 KHz/32 KHz£©

- ◊ÓµÕµƒFPGAŸY‘¥¿˚”√¬

- æØàÛ…˙≥…

- ¬º˛ïrÈg¥¡”õ

Ðõº˛π¶ƒÐ£∫

- ∆’Õ®ïrÁä∫ÕþÖΩÁïrÁä≤Ÿ◊˜

- ∂ÀµΩ∂À∫Õ¸c嶸c—”þtôC÷∆÷ß≥÷

- ‘⁄µ⁄2唣®“‘ôæW£©∫Õµ⁄3唣®IPv4£©Ω”ø⁄…œæ˘÷ß≥÷PTP

- À¸ø…“‘≈cHSR-PRP∫ÕæWπГ‘ôæWIPÉ»∫ÀΩY∫œ π”√

- VLAN÷ß≥÷

- π§òI≈‰÷√Œƒº˛£∫ƒ¨’J°¢Îä‘¥°¢Îä‘¥åç”√≥ÖÚIEC 61850-9-3°¢IEEE 802.1AS

- ∆˚Ðá≈‰÷√Œƒº˛£∫IEEE 802.1ASÕ®”√PTP£®gPTP£©≈‰÷√Œƒº˛

- ∆ÛòI≈‰÷√Œƒº˛/5G/Îä–≈≈‰÷√Œƒº˛£∫G.8265.1£¨G.8275.1∫ÕG.8275.2

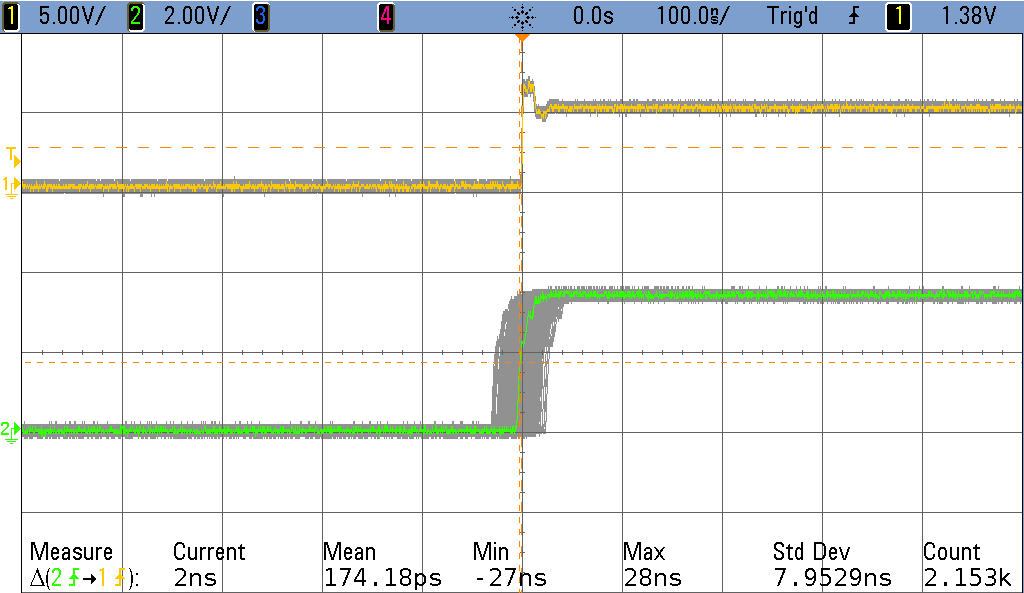

‘⁄IEEE 1588œµΩy÷–´@µ√µƒ◊ÓΩKæ´∂»»°õQ”⁄‘S∂ý“ÚÀÿ£®±æµÿïrÁ䵃Ól¬ ∫ÕŸ|¡ø£¨îµì˛Êú÷–ïrÈg¥¡µƒŒª÷√µ»£©°£◊˜ûÈÖ¢øº£¨œ¬àDÔ@ æ¡À…ÃòIGrandmaster‘Olj…˙≥…µƒPPS≈cZedboard Avnet Devopment Platfrom…˙≥…µƒPPS÷ÆÈgµƒúy¡ø’`≤Ó£¨Zedboard Avnet Devopment Platfrom‘⁄ARMÃé¿Ì∆˜÷–þ\––LinuxPTPÐõº˛∂—󣣨≤¢ π”√æ´¥_ïrÈgª˘µAþM––”≤º˛ðo÷˙ïrÈg¥¡£®+/-50 ns£©°£

Ö¢øº‘O”ã÷ß≥÷µƒ∞£∫

- SoC-e SMARTzynq brick£®Õ∆À]£©

- 嶔⁄∆‰À˚Xilinx/Avnet/SoC-e∞£¨Œ“ÇÉø…“‘÷π©œÞïrIPÉ»∫ÀþM––‘uπ¿°£

”˚¡ÀΩ‚∏¸∂ý–≈œ¢£¨’à¬ìœµŒ“ÇÉ£∫[email protected]°£ |